集成電路設(shè)計(jì) 現(xiàn)代科技的核心驅(qū)動(dòng)力

集成電路(IC)是現(xiàn)代電子設(shè)備的心臟,而集成電路設(shè)計(jì)則是這一心臟得以高效跳動(dòng)的關(guān)鍵所在。從智能手機(jī)到超級(jí)計(jì)算機(jī),從醫(yī)療設(shè)備到自動(dòng)駕駛汽車(chē),集成電路設(shè)計(jì)的身影無(wú)處不在,其重要性不言而喻。

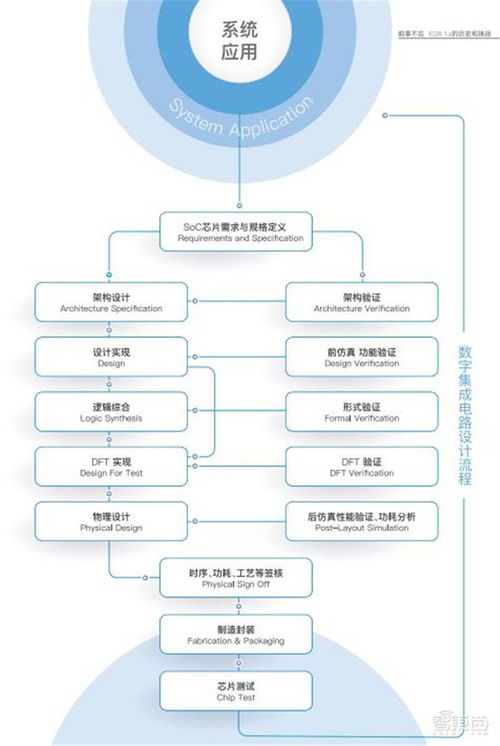

集成電路設(shè)計(jì)是一個(gè)將抽象的系統(tǒng)功能或算法,轉(zhuǎn)化為可在硅片上實(shí)現(xiàn)的物理版圖的復(fù)雜過(guò)程。這個(gè)過(guò)程通常可以概括為幾個(gè)主要階段:

1. 系統(tǒng)架構(gòu)與規(guī)格定義

設(shè)計(jì)的起點(diǎn)是明確需求。設(shè)計(jì)師需要確定芯片的功能、性能指標(biāo)(如速度、功耗)、成本目標(biāo)以及物理尺寸等。這類(lèi)似于為一座大廈繪制最初的設(shè)計(jì)藍(lán)圖。

2. 邏輯設(shè)計(jì)與驗(yàn)證

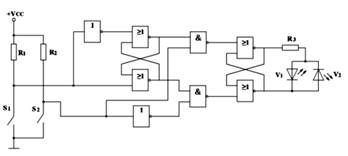

在此階段,設(shè)計(jì)師使用硬件描述語(yǔ)言(如Verilog或VHDL)來(lái)描述芯片的數(shù)字邏輯功能。通過(guò)仿真工具,可以驗(yàn)證邏輯設(shè)計(jì)的正確性,確保其行為符合預(yù)期。這一步是保證芯片功能正確的核心。

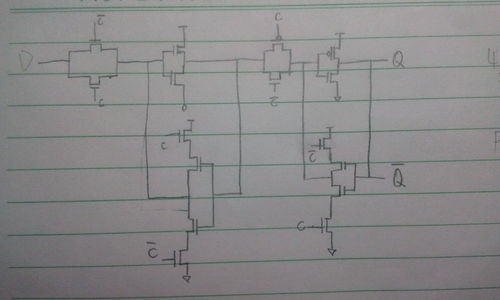

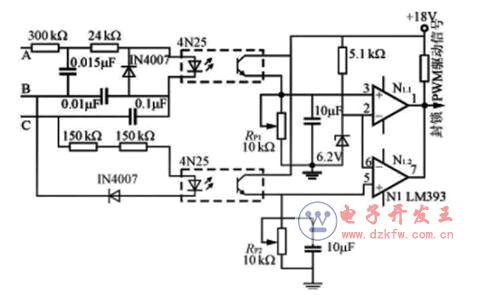

3. 電路設(shè)計(jì)

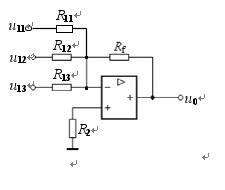

邏輯被進(jìn)一步細(xì)化到晶體管級(jí)別。模擬電路、存儲(chǔ)器單元、輸入輸出接口等都需要在這個(gè)階段精心設(shè)計(jì),以滿(mǎn)足特定的性能(如模擬精度、信號(hào)完整性)和功耗要求。

4. 物理設(shè)計(jì)

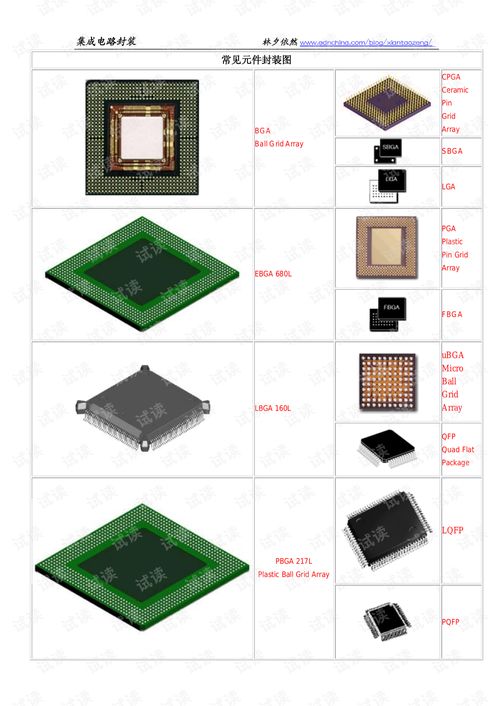

這是將電路圖“翻譯”成實(shí)際制造掩膜版圖的過(guò)程。它包括布局(在硅片上擺放各個(gè)元件)、布線(xiàn)(連接這些元件)、時(shí)序分析和功耗分析等。物理設(shè)計(jì)必須嚴(yán)格遵守芯片制造工廠的工藝規(guī)則,并優(yōu)化芯片的面積、性能和良率。

5. 驗(yàn)證與簽核

在最終交付制造前,設(shè)計(jì)必須通過(guò)一系列嚴(yán)格的檢查,包括功能驗(yàn)證、時(shí)序驗(yàn)證、物理驗(yàn)證(設(shè)計(jì)規(guī)則檢查、版圖與電路圖一致性檢查)等,以確保萬(wàn)無(wú)一失。

隨著技術(shù)的發(fā)展,集成電路設(shè)計(jì)也面臨著諸多挑戰(zhàn)與趨勢(shì):

- 工藝節(jié)點(diǎn)的持續(xù)微縮:晶體管尺寸不斷縮小至納米級(jí),帶來(lái)了量子效應(yīng)、漏電、制造成本飆升等巨大挑戰(zhàn)。

- 設(shè)計(jì)復(fù)雜度的爆炸式增長(zhǎng):如今一顆先進(jìn)芯片可集成數(shù)百億個(gè)晶體管,設(shè)計(jì)復(fù)雜度前所未有,對(duì)設(shè)計(jì)方法和工具提出了更高要求。

- 異構(gòu)集成與Chiplet(小芯片):為了平衡性能、成本和開(kāi)發(fā)周期,將不同工藝、不同功能的芯粒通過(guò)先進(jìn)封裝集成在一起,已成為重要趨勢(shì)。這改變了傳統(tǒng)的單片設(shè)計(jì)范式。

- EDA工具的智能化:人工智能和機(jī)器學(xué)習(xí)技術(shù)正被廣泛應(yīng)用于設(shè)計(jì)自動(dòng)化工具中,以輔助進(jìn)行設(shè)計(jì)空間探索、布局布線(xiàn)優(yōu)化和缺陷預(yù)測(cè),提升設(shè)計(jì)效率。

- 領(lǐng)域?qū)S眉軜?gòu)的興起:針對(duì)人工智能、汽車(chē)電子、高性能計(jì)算等特定領(lǐng)域,設(shè)計(jì)專(zhuān)用的處理器架構(gòu)(如NPU),以獲得遠(yuǎn)超通用處理器的能效比。

相關(guān)產(chǎn)品與生態(tài)

集成電路設(shè)計(jì)的成果最終體現(xiàn)為各類(lèi)芯片產(chǎn)品,主要包括:

- 微處理器(MPU)與微控制器(MCU):計(jì)算與控制的核心。

- 存儲(chǔ)器(Memory):如DRAM, Flash,用于數(shù)據(jù)存儲(chǔ)。

- 模擬與混合信號(hào)芯片:處理現(xiàn)實(shí)世界的連續(xù)信號(hào),如電源管理芯片、數(shù)據(jù)轉(zhuǎn)換器、射頻芯片等。

- 專(zhuān)用集成電路(ASIC):為特定用戶(hù)或應(yīng)用定制。

- 現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA):硬件可重構(gòu),提供設(shè)計(jì)靈活性。

整個(gè)設(shè)計(jì)過(guò)程高度依賴(lài)于電子設(shè)計(jì)自動(dòng)化(EDA)軟件、硅知識(shí)產(chǎn)權(quán)(IP)核以及先進(jìn)的晶圓制造與封裝測(cè)試產(chǎn)業(yè)鏈。這是一個(gè)資金、技術(shù)和人才高度密集的領(lǐng)域,也是全球高科技競(jìng)爭(zhēng)的戰(zhàn)略制高點(diǎn)。

總而言之,集成電路設(shè)計(jì)是連接創(chuàng)新想法與物理實(shí)現(xiàn)的橋梁,是推動(dòng)整個(gè)信息產(chǎn)業(yè)持續(xù)向前發(fā)展的引擎。它不僅是技術(shù)活,更是藝術(shù)與工程的完美結(jié)合,在不斷逼近物理極限的征程中,持續(xù)塑造著我們的未來(lái)。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.92wang.cn/product/49.html

更新時(shí)間:2026-02-08 04:09:32